## EE 508

#### Lecture 38

**High Frequency Filters**

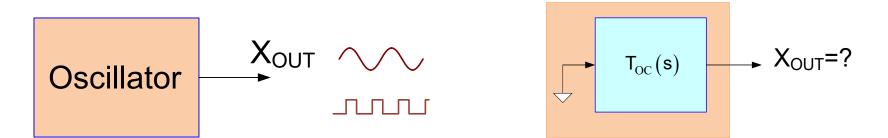

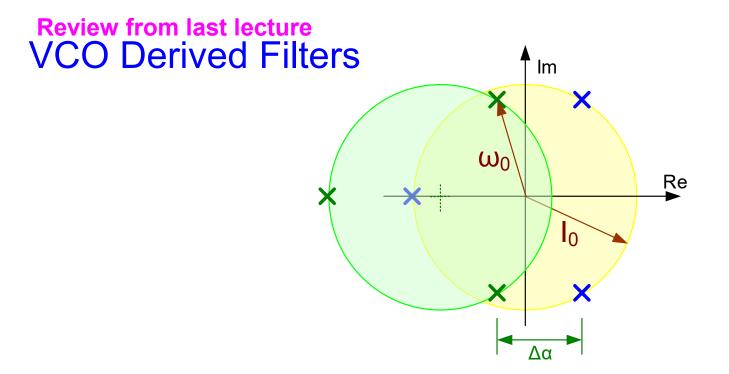

#### Review from last lecture What is the relationship, if any, between a filter and an oscillator or VCO?

- When power is applied to an oscillator, it initially behaves as a smallsignal linear network

- When operating linearly, the oscillator has poles (but no zeros)

- Poles are ideally on the imaginary axis or appear as cc pairs in the RHP

- There is a wealth of literature on the design of oscillators

- Oscillators often are designed to operate at very high frequencies

- If cc poles of a filter are moved to RHP is will become an oscillator

- Can oscillators be modified to become filters?

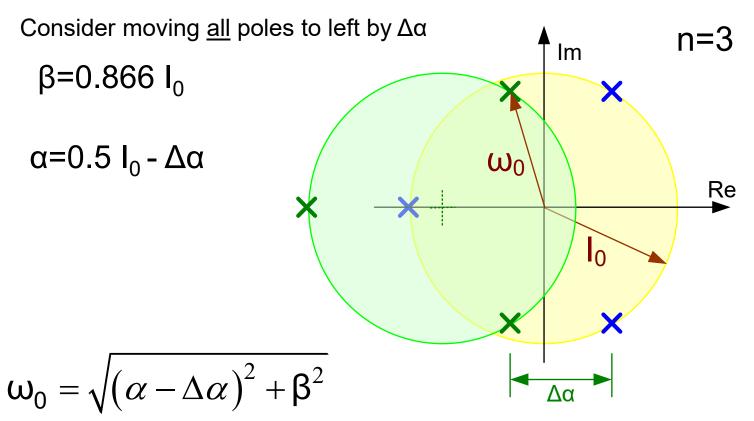

# Consider the following 3-pole situation

Poles of

$$D(s) = s^n + I_0^n$$

So, to get a high  $\omega_0$ , want  $\beta$  as large as possible

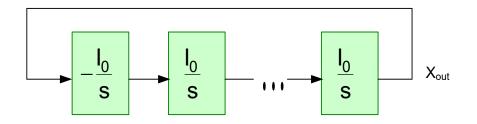

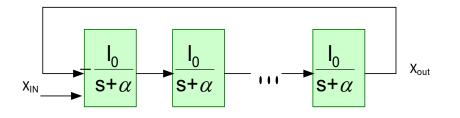

#### Review from last lecture Consider a cascaded integrator loop comprised of n integrators

$$X_{OUT} = -\left(\frac{I_0}{s}\right)^n X_{OUT}$$

$$X_{OUT}\left(s^n + I_0^n\right) = 0$$

$$D(s) = s^n + I_0^n$$

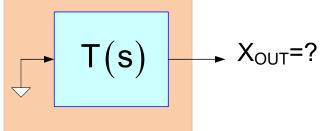

- Most if not all oscillators can be modified to form a narrow-band bandpass filter

- Modification involves

- ✓ adding loss so that the pole-pair with the largest real component is in the LHP

- ✓ Introducing input to form a filter

- Can provide new filter architectures and benefit from desirable properties of the oscillator

- High frequency filters can be obtained from high frequency oscillators

#### Review from last lecture Inputs to Oscillator-Derived Filters:

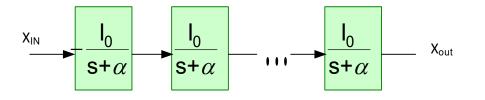

Most applicable to designing 2<sup>nd</sup>-order high frequency narrow band bandpass filters

- Add loss to delay stages

- Multiple Input Locations Often Possible

- Natural Input is Input to delay stage

- Often Just Salvage Stages (drop feedback loop)

- Natural input is input to delay stage

## High Frequency Filter Design

- Architecture selection is critical

- At high frequencies, simplicity of the structures is important

- Parasitic capacitances and their relationship to the time constants that can be achieved provide the ultimate limit on speed

- Will limit discussions to "inductorless" structures

## High Frequency Filter Design

Following two methods will provide highest frequency of operation

- Degenerate VCOs

- Simple high-frequency integrator-based filters

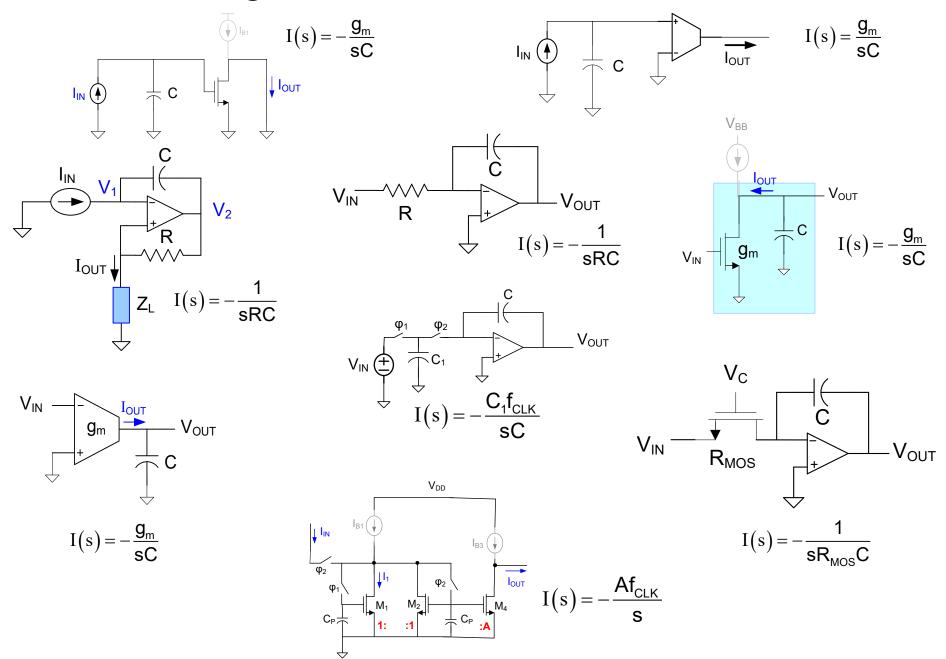

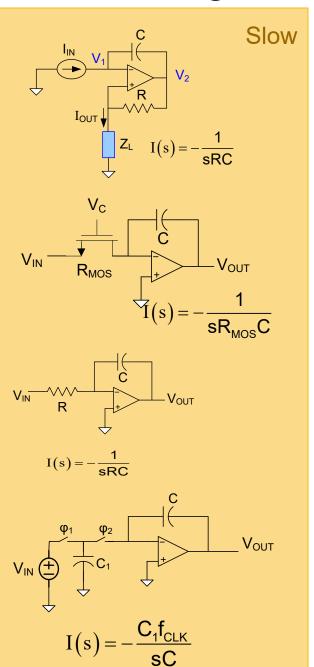

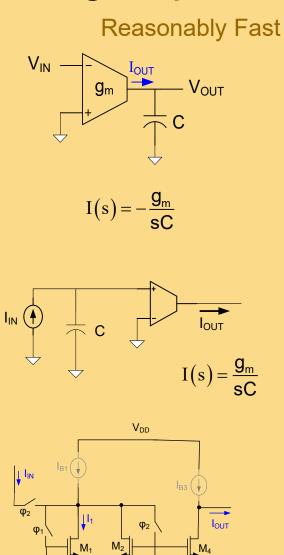

#### **Integrator Architecture Selection**

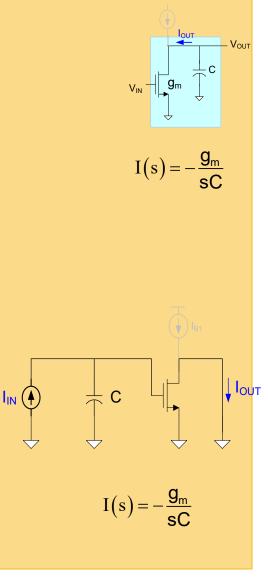

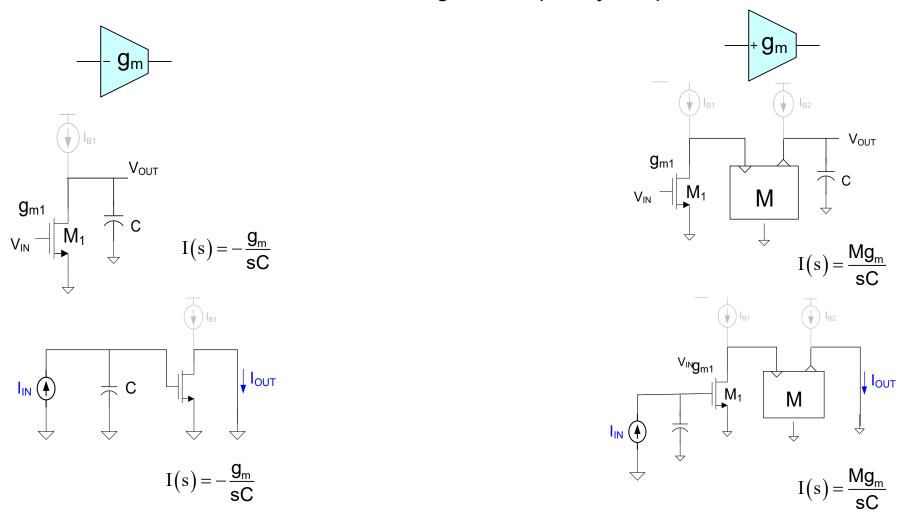

#### Integrators for High-Speed Operation

$I(s) = -\frac{Af_{CLK}}{s}$

Very Fast

Structures of choice for highest-frequency of operation

Some authors focus on voltage mode and others on current mode But overall structures and performance appears to be identical

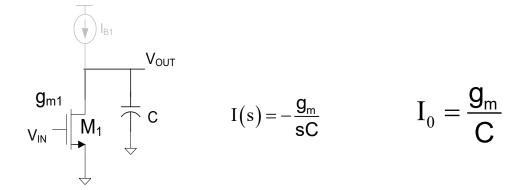

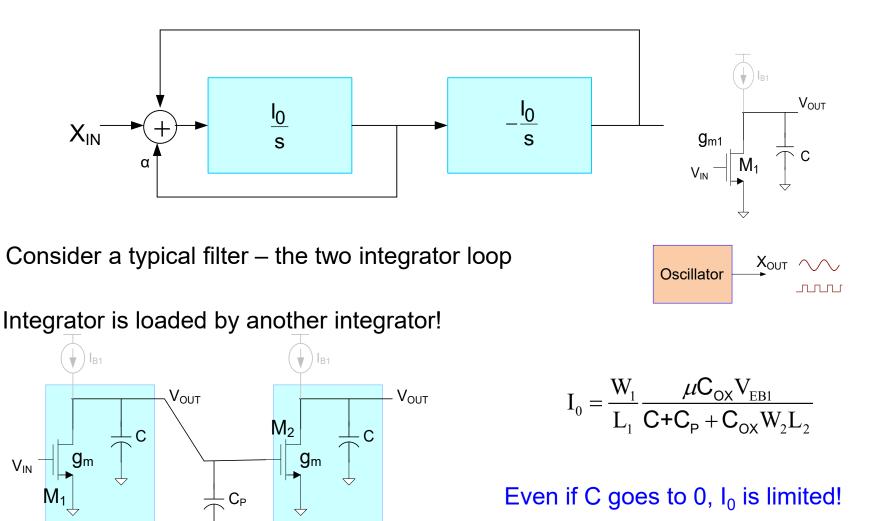

Recall:  $\omega_0$  for integrator-based filters generally proportional to I<sub>0</sub>

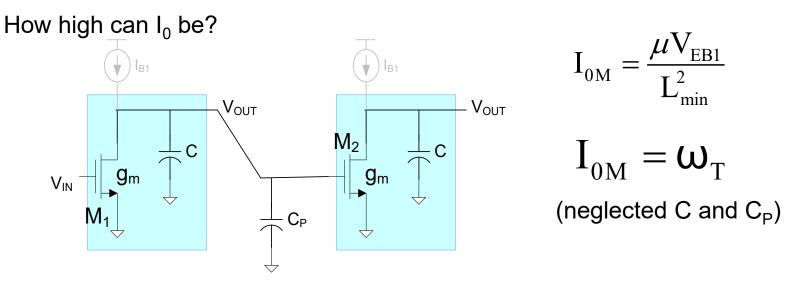

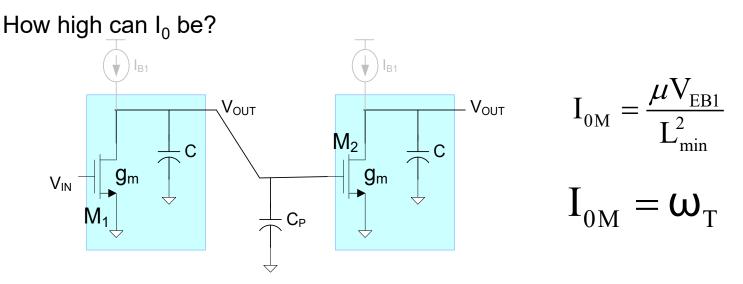

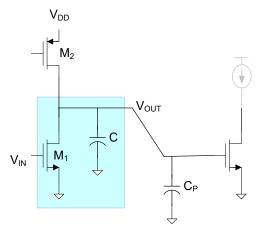

How high can  $I_0$  be?

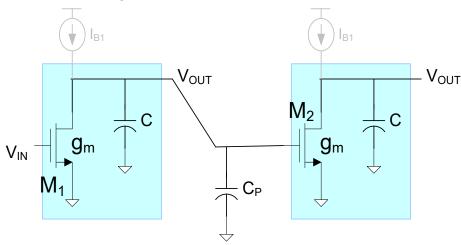

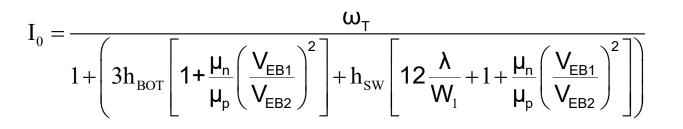

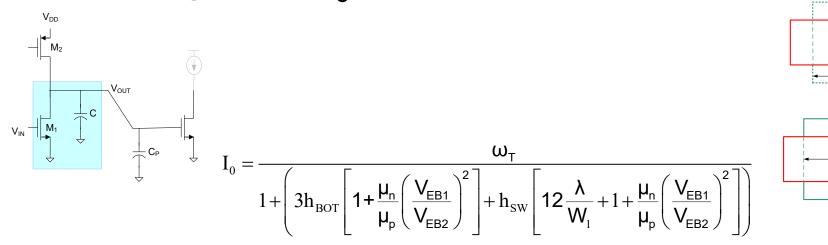

$$I_0 = \frac{W}{L} \frac{\mu C_{OX} V_{EB}}{C}$$

Looks like we can make  $\rm I_0$  as large as we want by making  $\rm V_{EB}$  large, C small, L small, and W large

How high can  $I_0$  be?

Even if C goes to 0,  $I_0$  is limited!

$C_{P}$  is the parasitic capacitances on the output node

How high can  $I_0$  be?

$$\mathbf{I}_{0} = \frac{\mathbf{W}_{1}}{\mathbf{L}_{1}} \frac{\mu \mathbf{C}_{\mathsf{OX}} \mathbf{V}_{\mathsf{EB1}}}{\mathbf{C} + \mathbf{C}_{\mathsf{P}} + \mathbf{C}_{\mathsf{OX}} \mathbf{W}_{2} \mathbf{L}_{2}}$$

Setting C to 0 and assuming  $C_p$  is small,

$$I_0 = W_1 / L_1 \frac{\mu C_{OX} V_{EB1}}{C_{OX} W_2 L_2}$$

$$I_0 = \frac{\mu W_1 V_{EB1}}{W_2 L_1 L_2}$$

Assuming the integrator stages are identical, it follows that

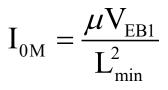

$$I_0 = \frac{\mu V_{EB1}}{L_{min}^2}$$

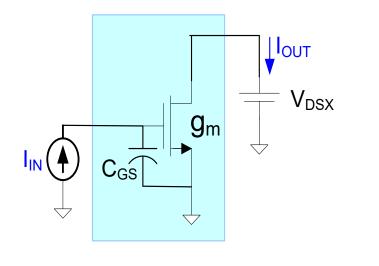

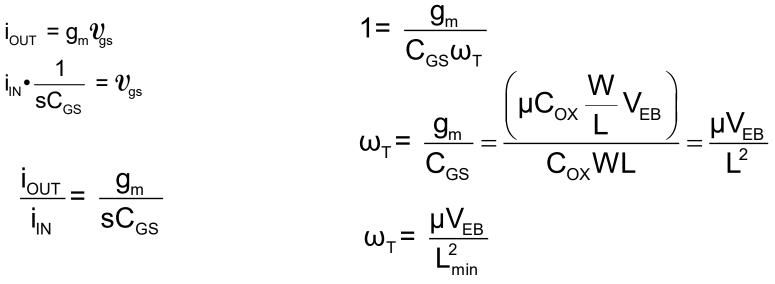

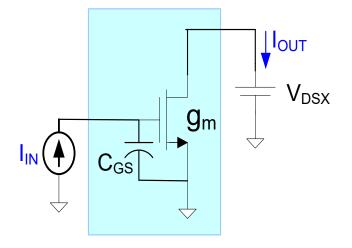

#### Transition (transit) frequency $(f_T)$ of a process

The transit frequency of a process is the frequency where the short-circuit current gain of the common-source configuration drops to 1.

Journal of the Korean Physical Society, Vol. 40, No. 1, January 2002, pp. 45~48

Fig. 7. (a) Maximum stable gain (MSG) and maximum available gain (MAG) for different channel lengths and (b) the cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  as functions of the channel length.

### Transition (transit) frequency $(f_T)$ of a process

The transit frequency of a process is the frequency where the short-circuit current gain of the common-source configuration drops to 1.

$$\omega_{T} = \frac{\mu V_{EB}}{L_{min}^{2}}$$

This is dependent upon  $V_{EB}$

Does not include effects of diffusion capacitances or overlap capacitances  $f_{MAX}$  is another figure that characterizes the speed of a process

Speed of operation increases with  $V_{\text{EB1}}$

$V_{\text{EB1}}$  is limited by signal swing requirements and  $V_{\text{DD}}$

Symmetric Signal Swing:

$$V_{SW} \cong \min\{V_{DD} - V_{OQ}, V_{OQ} - (V_T + 100mV)\}$$

$$V_{OQ} = V_T + V_{EB}$$

$$V_{SW} \cong \min\{V_{DD} - V_T - V_{EB}, V_T + V_{EB} - (V_T + 100mV)\}$$

Speed of operation increases with  $V_{\text{EB}}$

$V_{EB}$  is limited by signal swing requirements and  $V_{DD}$

Signal Swing:

$$V_{DD} - V_{T} - V_{EB} = V_{T} + V_{EB} - (V_{T} + 100 \text{mV})$$

$$V_{EB} = \frac{V_{DD} + 100 \text{mV} - V_{T}}{2}$$

$$I_{OMAX} \cong \frac{\mu (V_{DD} + 100 \text{mV} - V_{T})}{2L_{min}^{2}}$$

#### How high can $I_0$ be?

How much power is required to realize  $I_{0MAX}$ ?

$$P_{\text{QPT}} = V_{\text{DD}} I_{\text{D}}$$

$$P_{\text{QPT}} = V_{\text{DD}} \frac{\mu C_{\text{OX}} W_1 V_{\text{EB1}}^2}{2L_{\text{min}}}$$

Note this is proportional to  $W_1$

$$\begin{split} \mathbf{P}_{\text{QPT}} &= \mathbf{V}_{\text{DD}} \frac{\mu \mathbf{C}_{\text{OX}} \mathbf{W}_{\text{min}} \mathbf{V}_{\text{EB1}}^2}{2 \mathbf{L}_{\text{min}}} \overset{\mathbf{W}_{\text{min}} = \mathbf{L}_{\text{min}}}{\cong} \mathbf{V}_{\text{DD}} \frac{\mu \mathbf{C}_{\text{OX}} \mathbf{V}_{\text{EB1}}^2}{2} \\ &= \mathbf{V}_{\text{DD}} \frac{\mu \mathbf{C}_{\text{OX}}}{2} \left( \frac{\mathbf{V}_{\text{DD}} + 100 \text{mV} - \mathbf{V}_{\text{T}}}{2} \right)^2 \overset{\mathbf{V}_{\text{T}} = 0.25 \text{V}_{\text{DD}}}{\cong} \mathbf{V}_{\text{DD}} \frac{\mu \mathbf{C}_{\text{OX}}}{2} \left( \frac{0.75 \text{V}_{\text{DD}}}{2} \right)^2 \cong .07 \mu \mathbf{C}_{\text{OX}} \mathbf{V}_{\text{DD}}^3 \end{split}$$

$$\mathbf{I}_{0} = \frac{\mu \mathbf{C}_{\mathsf{OX}} \mathbf{W}_{1} / \mathbf{L}_{1} \mathbf{V}_{\mathsf{EB1}}}{\mathbf{C} + \mathbf{C}_{\mathsf{P}} + \mathbf{C}_{\mathsf{OX}} \mathbf{W}_{1} \mathbf{L}_{1}}$$

Neglecting Cp and C, obtained

$I_{0M} = \omega_T$

Note this is independent of  $W_1$

$$I_{\text{OMAX}} \cong \frac{\mu (V_{\text{DD}} + 100 \text{mV} - V_{\text{T}})}{2L_{\text{min}}^2}$$

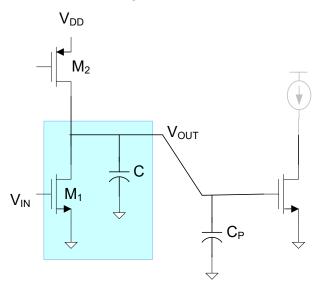

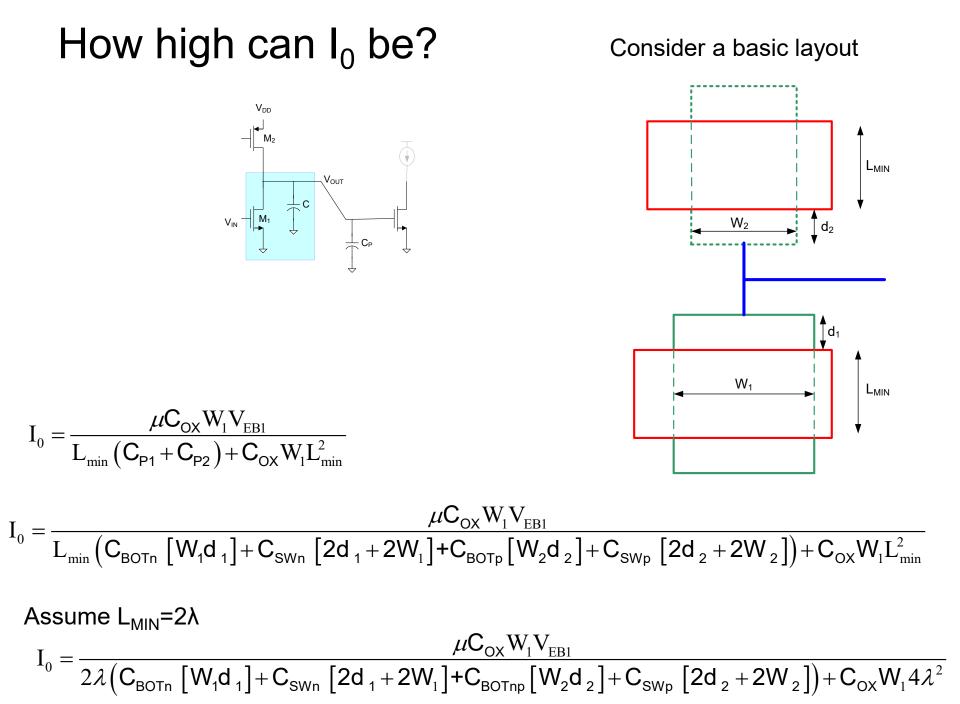

#### How high can $I_0$ be?

Consider again Cp and recall:

$$\mathbf{I}_{0} = \frac{\mathbf{W}_{1}}{\mathbf{L}_{1}} \frac{\mu \mathbf{C}_{\mathsf{OX}} \mathbf{V}_{\mathsf{EB1}}}{\mathbf{C} + \mathbf{C}_{\mathsf{P}} + \mathbf{C}_{\mathsf{OX}} \mathbf{W}_{2} \mathbf{L}_{2}}$$

C<sub>P</sub> will modestly reduce the speed of the circuit

$$I_0 = \frac{\mu \boldsymbol{C}_{\mathsf{OX}} \boldsymbol{W}_1 \boldsymbol{V}_{\mathsf{EB1}}}{\boldsymbol{L}_{\mathsf{min}} \boldsymbol{C}_{\mathsf{P}} + \boldsymbol{C}_{\mathsf{OX}} \boldsymbol{W}_1 \boldsymbol{L}_{\mathsf{min}}^2}$$

Consider the diffusion capacitances on M<sub>1</sub> and M<sub>2</sub>

$$I_{0} = \frac{\mu C_{\text{OX}} W_{1} V_{\text{EB1}}}{L_{\text{min}} \left( C_{\text{P1}} + C_{\text{P2}} \right) + C_{\text{OX}} W_{1} L_{\text{min}}^{2}}$$

$$\boldsymbol{I}_{0} = \boldsymbol{W}_{1} \, / \, \boldsymbol{L}_{1} \frac{\boldsymbol{\mu} \boldsymbol{C}_{\mathsf{OX}} \boldsymbol{V}_{\mathsf{EB1}}}{\boldsymbol{C} \textbf{+} \boldsymbol{C}_{\mathsf{P}} \, \textbf{+} \, \boldsymbol{C}_{\mathsf{OX}} \boldsymbol{W}_{1} \boldsymbol{L}_{1}}$$

Neglecting Cp and C, obtained

$$I_{0M} = \omega_T$$

$$I_{0M} = \frac{\mu V_{EB1}}{L_{min}^2}$$

$$I_{OMAX} \cong \frac{\mu (V_{DD} + 100mV - V_T)}{2L_{min}^2}$$

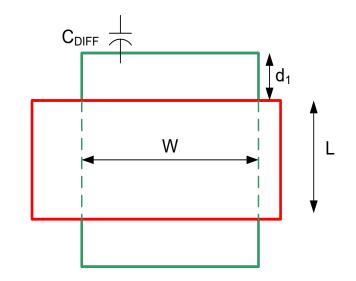

#### How high can $I_0$ be?

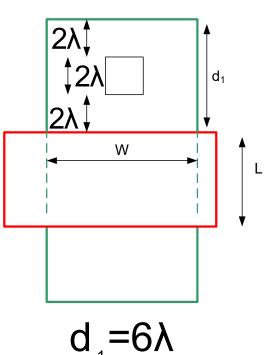

The parasitic diffusion capacitances are strongly layout dependent

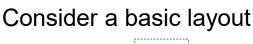

Consider a basic layout of a transistor

The capacitance density along the sw of the drain is usually somewhat less than that along the outer perimeters but may not easily be modeled separately

Assuming the same, drain diffusion capacitance of a transistor is given by

$$C_{DIFF} = C_{BOT} \left[ W d_{1} \right] + C_{SW} \left[ 2d_{1} + 2W \right]$$

$C_{BOT}$  is the bottom diffusion capacitance density  $C_{SW}$  is the sidwall diffusion capacitance density

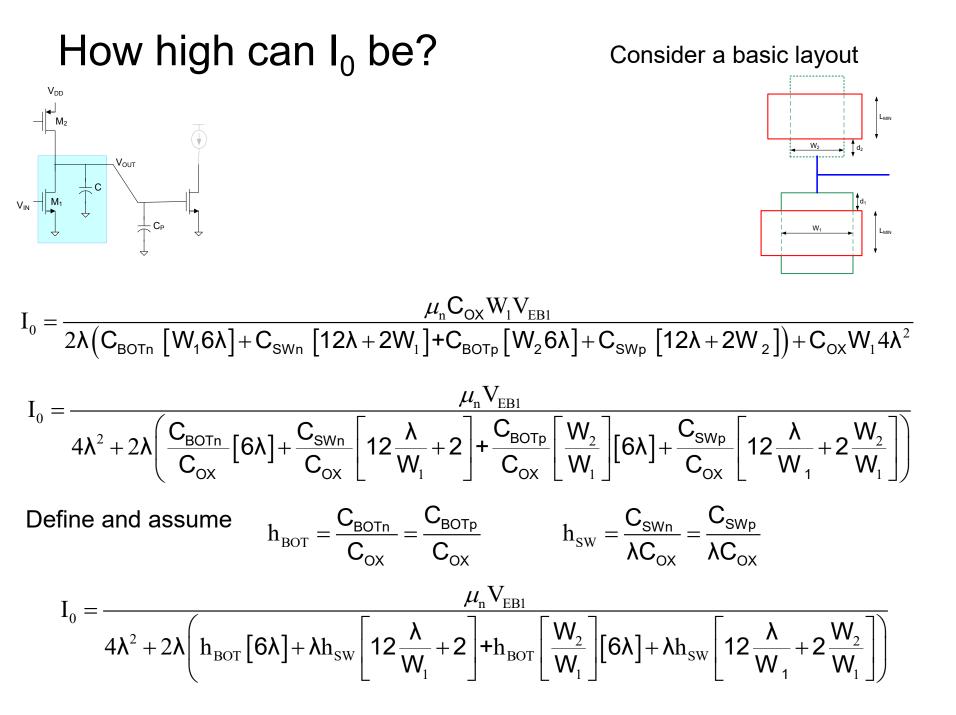

How high can  $I_0$  be?

Consider a basic layout of a transistor

Assume  $d_1=6\lambda$

$I_{0} = \frac{\mu C_{OX} W_{1} V_{EB1}}{2\lambda \left( C_{BOTn} \left[ W_{1} d_{1} \right] + C_{SWn} \left[ 2d_{1} + 2W_{1} \right] + C_{BOTp} \left[ W_{2} d_{2} \right] + C_{SWp} \left[ 2d_{2} + 2W_{2} \right] \right) + C_{OX} W_{1} 4\lambda^{2}}$

$I_{0} = \frac{\mu C_{\text{OX}} W_{1} V_{\text{EB1}}}{2\lambda \left( C_{\text{BOTn}} \left[ W_{1} 6\lambda \right] + C_{\text{SWn}} \left[ 12\lambda + 2W_{1} \right] + C_{\text{BOTp}} \left[ W_{2} 6\lambda \right] + C_{\text{SWp}} \left[ 12\lambda + 2W_{2} \right] \right) + C_{\text{OX}} W_{1} 4\lambda^{2}$

$W_2$

W<sub>1</sub>

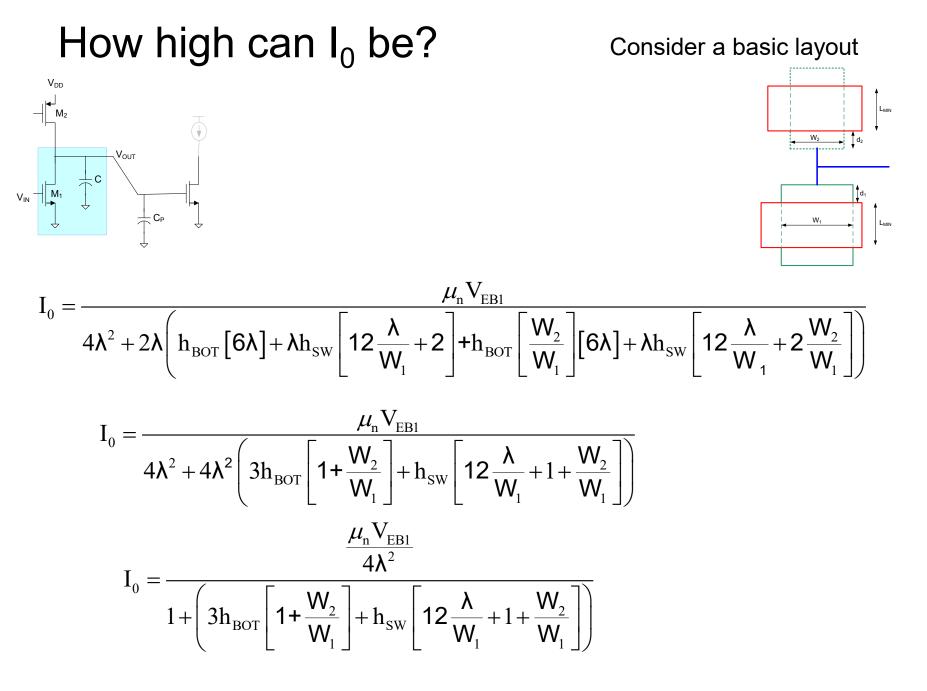

#### How high can $I_0$ be?

#### Consider a basic layout

$W_2$

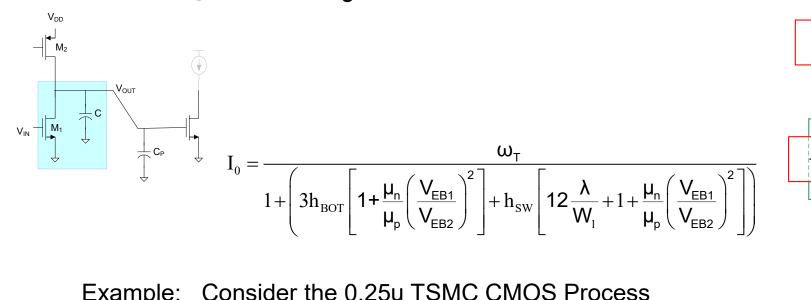

Example: Consider the 0.25u TSMC CMOS Process

$$C_{ox} = 5.8 \text{fF}/\mu^2$$

$\frac{\mu_n}{\mu_p} = 4.1$  $C_{swn} = .440 \text{fF}/\mu$  $\mu_p$  $C_{swp} = .350 \text{fF}/\mu$  $\mu_n = 3.74 \text{E}10$  $C_{swp} = 1.8 \text{fF}/\mu^2$  $\lambda = 0.125 \mu$

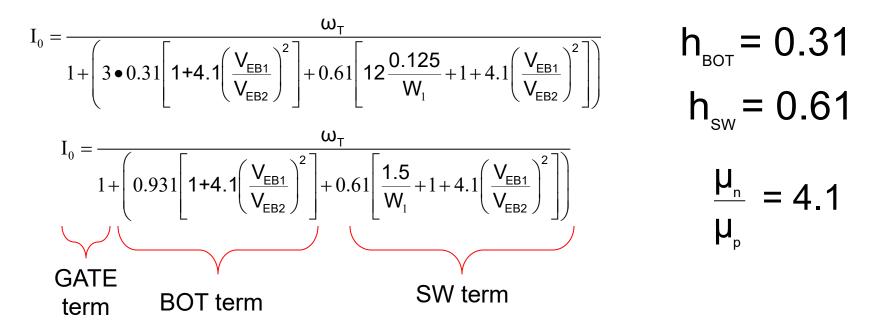

$h_{BOT} = \frac{C_{BOTn}}{C_{OX}} = \frac{C_{BOTp}}{C_{OX}}$  $h_{BOT} = 0.31$  $h_{SW} = \frac{C_{SWn}}{\lambda C_{OX}} = \frac{C_{SWp}}{\lambda C_{OX}}$

$h_{sw} = 0.61$

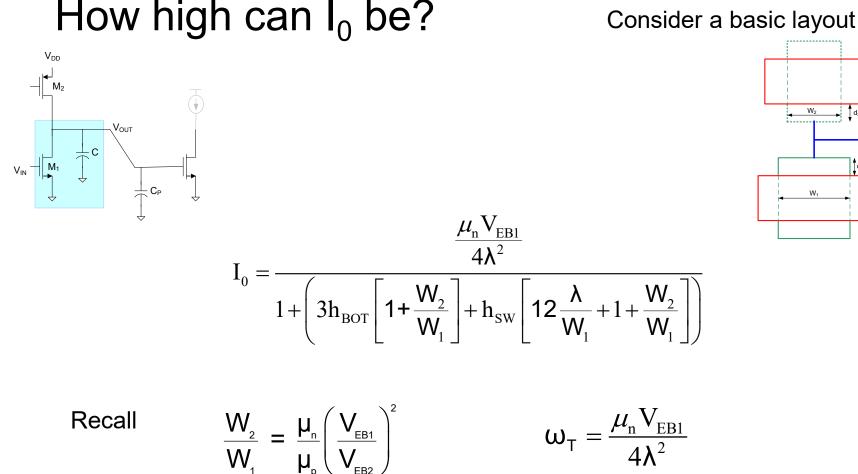

#### How high can $I_0$ be?

#### Consider a basic layout

$W_2$

# Example: Consider the 0.25u TSMC CMOS Process $I_{0} = \frac{\omega_{T}}{1 + \left(0.93 \left[1 + 4.1 \left(\frac{V_{EB1}}{V_{EB2}}\right)^{2}\right] + 0.61 \left[\frac{1.5}{W_{1}} + 1 + 4.1 \left(\frac{V_{EB1}}{V_{EB2}}\right)^{2}\right]\right)}$

#### How high can $I_0$ be?

#

GATE

term

$V_{DD}$

If W<sub>1</sub>=1.5u and V<sub>EB1</sub>=V<sub>EB2</sub>  $I_0 = \frac{\omega_T}{1 + (4.73 + 4.03)} = .102\omega_T$

BOT term

- Designer has control of V<sub>EB1</sub> and V<sub>EB2</sub>

The diffusion consolitones term considering

- The diffusion capacitance term can dominate the  $C_{\rm GS}$  term

- The SW capacitance can be the biggest contributor to the speed limitations

- A factor of 10 or even much more reduction in speed is possible due to the diffusion parasitics and layout

- Maximizing  $W_1$  will minimize  $I_0$  but power will get very large for marginal improvement in speed

SW term

## Stay Safe and Stay Healthy !

# End of Lecture 38